# APPENDIX 4: ACTIVITIES LAUNCHED IN 2024 FOR THE INITIATIVE PART

Version 8

## CONTENTS

| <b>APPENDIX 4: A</b> | CTIVITIES LAUNO | <b>CHED IN 2024 FO</b> | R THE INITIAT | IVE PART |

|----------------------|-----------------|------------------------|---------------|----------|

| 1                    |                 |                        |               |          |

|                      |                 |                        |               |          |

| 1. | ACTIVITIES 2024 INITIATIVE PART7                                                   |

|----|------------------------------------------------------------------------------------|

| 2. | TECHNICAL DESCRIPTION OF THE CALLS7                                                |

|    | 2.1. Chips-2024 CCC-1: Competence centres                                          |

|    | 2.1.1. Context                                                                     |

|    | 2.1.2. Expected outcomes                                                           |

|    | 2.1.3. Scope                                                                       |

|    | 2.1.4. Access to the Chips CC                                                      |

|    | 2.1.5. Consortia for CC                                                            |

|    | 2.1.6. Size, funding and access to services                                        |

|    | 2.1.7. Type of Action                                                              |

|    | 2.1.8. Admissibility                                                               |

|    | 2.1.9. Eligibility and selection process                                           |

|    | 2.1.10. Financial and operational capacity and exclusion                           |

|    | 2.1.11. Award criteria used for open calls                                         |

|    | 2.1.12. Score                                                                      |

|    | 2.2. Chips-2024-CCC-2: Support to the European Network of Chips Competence Centres |

|    | 2.2.1. Expected Outcomes                                                           |

|    | 2.2.2. Scope                                                                       |

|    | 2.2.3. Type of Action                                                              |

|    | 2.2.4. Admissibility                                                               |

|    | 2.2.5. Eligibility                                                                 |

|    | 2.2.6. Financial and operational capacity and exclusion                            |

|    | 2.2.7. Evaluation procedure                                                        |

|    | 2.2.8. Award criteria                                                              |

|    | 2.2.9. Score                                                                       |

|    | 2.3. Chips-2024-CPL-5: Pilot Line on Advanced Photonic Integrated Circuits 21      |

|    | 2.3.1. Context                                                                     |

| 2.3.2. Expected Outcomes                                                                                                           | 22           |

|------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2.3.3. Scope                                                                                                                       | 23           |

| 2.3.4. Specific provisions applicable to Calls for pilot lines                                                                     | 24           |

| 2.3.5. Other general provisions                                                                                                    | 26           |

| 2.4. Chips-2024-CDP-1: Design platform                                                                                             | 27           |

| 2.4.1. Context                                                                                                                     | 27           |

| 2.4.2. Expected outcomes                                                                                                           | 29           |

| 2.4.3. Scope                                                                                                                       | 30           |

| 2.4.4. Type of Action                                                                                                              | 34           |

| 2.4.5. Specific Provisions applicable to the Call for Design Platfor                                                               | m34          |

| 2.4.6. Other general Provisions                                                                                                    | 38           |

| Call for Quantum Pilot Lines                                                                                                       | 40           |

| 2.5. Chips-QAC-1: Call for establishing Framework Partnership for developing Quantum Chip Technology for stability Pilot Lines     | · ·          |

| 2.5.1. Context                                                                                                                     | 41           |

| 2.5.2. Expected Outcomes                                                                                                           | 42           |

| 2.5.3. Scope                                                                                                                       | 43           |

| 2.5.4. Eligibility                                                                                                                 | 45           |

| 2.5.5. STEP and Sovereignty Seal                                                                                                   | 45           |

| 2.5.6. Specific provisions applicable to this Call                                                                                 | 46           |

| 2.5.7. Other general provisions                                                                                                    | 47           |

| 2.6. Chips-QAC-2: Call for establishing Framework Agreement(s) for developing Quantum Chip Technology for Trapped Ions Pilot Lines | high-quality |

| 2.6.1. Context                                                                                                                     | 49           |

| 2.6.2. Expected outcomes.                                                                                                          | 49           |

| 2.6.3. Collaborations                                                                                                              | 50           |

| 2.6.4. Scope                                                                                                                       | 50           |

| 2.6.5. Eligibility                                                                                                                 | 52           |

| 2.6.6. STEP and sovereignty seal                                                                                                   | 53           |

| 2.6.7. Specific provisions applicable to this Call                                                                                 | 53           |

| CALL FOR PILOT LINES (CPL)                                                                                                         | 56           |

| <b>3.</b> | INTRODUCTION – CONTEXT AND BACKGROUND                                                                        | 57 |

|-----------|--------------------------------------------------------------------------------------------------------------|----|

|           | 3.1. LEGAL FRAMEWORK                                                                                         | 57 |

|           | 3.1.1. Budget                                                                                                | 58 |

|           | 3.1.2. The overall implementation process                                                                    | 59 |

|           | 3.2. OBJECTIVES                                                                                              | 64 |

|           | 3.2.1. Description of the pilot line                                                                         | 65 |

|           | 3.2.2. Budget available                                                                                      | 65 |

|           | 3.3. CONTENTS OF THE APPLICATION                                                                             | 66 |

|           | 3.4. ADMISSIBILITY REQUIREMENTS                                                                              | 70 |

|           | 3.4.1. Admissibility requirements for the Call for Expression of Interest.                                   | 70 |

|           | 3.4.2. Admissibility requirements for the Call for Proposals for S integration and process development       | _  |

|           | 3.4.3. Admissibility requirements for the Call for Proposals for Opera activities of the pilot line          |    |

|           | 3.5. ELIGIBILITY CRITERIA                                                                                    | 71 |

|           | 3.5.1. Eligibility criteria for the Call for Expression of Interest                                          | 71 |

|           | 3.5.2. Eligibility criteria for the Call for Proposals for Set-up, integration process development           |    |

|           | 3.5.3. Eligibility criteria for the Call for Proposals for Operational activit the pilot line                |    |

|           | 3.6. EXCLUSION CRITERIA                                                                                      | 73 |

|           | 3.6.1. Exclusion criteria for the Call for Expression of Interest                                            | 73 |

|           | 3.6.2. Exclusion and selection criteria for the Call for Proposals for S integration and process development |    |

|           | 3.6.3. Selection and exclusion criteria for the Call for Proposals for Opera activities of the pilot line    |    |

|           | 3.6.4. Rejection from the Call                                                                               | 75 |

|           | 3.7. EVALUATION CRITERIA                                                                                     | 75 |

|           | 3.7.1. Evaluation criteria for the Call for Expression of Interest                                           | 75 |

|           | 3.7.2. Evaluation criteria for the Call for Proposals for Set-up, integration process development            |    |

|           | 3.7.3. Evaluation criteria for the Call for Proposals for Operational activi the pilot line                  |    |

| 3.8. OVERVIEW OF THE EVALUATION A                                                      | AND SELECTION      |

|----------------------------------------------------------------------------------------|--------------------|

| PROCEDURE                                                                              | 79                 |

| 3.8.1. Evaluation procedure                                                            | 79                 |

| 3.8.2. Selection                                                                       | 79                 |

| 3.8.3. Communication                                                                   | 80                 |

| 3.9. TIMETABLE                                                                         | 81                 |

| 3.10. PROCEDURE FOR THE SUBMISSION OF APPL                                             | ICATIONS82         |

| 3.10.1. For the Call for Expression of Interest                                        | 82                 |

| 3.10.2. For the Call HE                                                                | 82                 |

| 3.10.3. For the Call DEP                                                               | 82                 |

| 3.10.4. Other submission related comments                                              | 82                 |

| DESCRIPTION OF THE CALL FOR DESIGN PLATFORM (C                                         | CDP)84             |

| 4. INTRODUCTION                                                                        | 85                 |

| 4.1. Legal framework                                                                   | 85                 |

| 4.1.1. Budget                                                                          | 86                 |

| 4.1.2. Context and background                                                          | 86                 |

| 4.1.3. The overall implementation process                                              | 89                 |

| 4.2. OBJECTIVES                                                                        | 94                 |

| 4.2.1. Description of the Design Platform                                              | 95                 |

| 4.3. BUDGET AVAILABLE                                                                  | 95                 |

| 4.4. CONTENT OF THE APPLICATION                                                        | 96                 |

| 4.4.1. General provisions                                                              | 96                 |

| 4.4.2. Hosting provisions                                                              | 98                 |

| 4.5. ADMISSIBILITY REQUIREMENTS                                                        | 99                 |

| 4.5.1. Admissibility requirements for the Call for Express                             | sion of Interest99 |

| 4.5.2. Admissibility requirements for the Call for coordination of the Design Platform |                    |

| 4.6. ELIGIBILITY CRITERIA                                                              | 100                |

| 4.6.1. Eligibility criteria for the Call for Expression of Int                         | terest100          |

| 4.6.2. Eligibility criteria for the Call for Proposals for the Design Platform         |                    |

| 4.7. EXCLUSION CRITERIA                                                                | 101                |

| 4.7.1. Exclusion criteria for the Call for Expression of Interest101                                           |

|----------------------------------------------------------------------------------------------------------------|

| 4.7.2. Selection and exclusion criteria for the Call for Proposals for the coordination of the Design Platform |

| 4.7.3. Rejection from the Call                                                                                 |

| 4.8. EVALUATION CRITERIA104                                                                                    |

| 4.8.1. Evaluation criteria for the Call for Expression of Interest104                                          |

| 4.8.2. Evaluation criteria for the Call for Proposals for the coordination of the Design Platform              |

| 4.9. OVERVIEW OF THE EVALUATION AND SELECTION PROCEDURE                                                        |

| 4.9.1. Evaluation procedure                                                                                    |

| 4.9.2. Selection                                                                                               |

| 4.9.3. Communication                                                                                           |

| 4.10. TIMETABLE                                                                                                |

| 4.11. PROCEDURE FOR THE SUBMISSION OF APPLICATIONS109                                                          |

| 4.11.1. For the Call for Expression of Interest                                                                |

| 4.11.2. For the Digital Europe Programme Call                                                                  |

| 4.11.3. Other submission related comments                                                                      |

| TECHNICAL ANNEXES                                                                                              |

| ANNEXES                                                                                                        |

| ANNEX A – DESIGN ENABLEMENT TEAMS112                                                                           |

| ANNEX B – CLOUD SERVICES113                                                                                    |

| ANNEX C - START-UP INCUBATION AND ACCELLERATION PROGRAMMES                                                     |

| ANNEX I: LETTER OF INTENT FOR COMPETENCE CENTRE CALL115                                                        |

| ANNEX II: GENERAL DIGITAL EUROPE PROGRAMME CONDITIONS117                                                       |

| ANNEX III: GENERAL HORIZON EUROPE CONDITIONS124                                                                |

| ANNEX IV- ART. 12(6) OF REGULATION (EU) 2021/694129                                                            |

## 1. ACTIVITIES 2024 INITIATIVE PART

This appendix foresees the launch of the following calls with an estimated EU expenditure of up to EUR 330 million:

- 1. DIGITAL-Chips-2024-SG-CCC-1: Competence centres.

- 2. DIGITAL-Chips-2024-CSA-CCC-2: Support to the European Network of Chips Competence Centres

- 3. DIGITAL-Chips-2024-CfEoI-CPL-5: Pilot Line on Advanced Photonic Integrated Circuits

- 4. HORIZON-Chips-2024-RIA-CPL-5: Pilot Line on Advanced Photonic Integrated Circuits

- 5. DIGITAL-Chips-2024-SG-CPL-5: Pilot Line on Advanced Photonic Integrated Circuits.

- 6. DIGITAL-Chips-2024-CfEoI-CDP-1: Design Platform

- 7. DIGITAL-Chips-2024-CSA-CDP-1: Design Platform

- 8. HORIZON-JU-Chips-2024-FPA-QAC-1: Call for establishing Framework Partnership Agreements for developing Quantum Chip Technology for stability Pilot Lines.

- 9. HORIZON-JU-Chips-2024-FPA-QAC-2: Call for establishing Framework Partnership Agreement(s) for developing Quantum Chip Technology for high-quality Trapped Ions Pilot Lines.

## 2. TECHNICAL DESCRIPTION OF THE CALLS

## 2.1. Chips-2024 CCC-1: Competence centres

| Chips-2024-CCC-1                 |                                                                                            |  |

|----------------------------------|--------------------------------------------------------------------------------------------|--|

| DIGITAL-Chips-2024-SG-CCC-1      | EU Expenditure = <i>Max. EURO 116 Mio</i>                                                  |  |

| Security                         | Call restricted on the basis of Article 12(6) of the Regulation (EU) 2021/694 <sup>1</sup> |  |

| Publication date                 | 04th Jul 2024                                                                              |  |

| Deadline Submission of proposals | 2 <sup>nd</sup> Oct. 2024 at 17:00 Brussels Time                                           |  |

#### **2.1.1.** Context

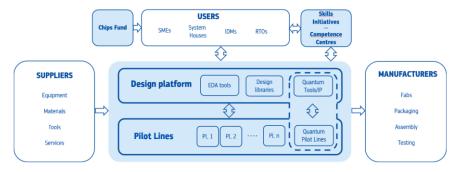

Competence centres in semiconductors (aka "Chips Competence Centres" or "Chips CCs") will play an essential role in the Chips for Europe Initiative. The centres will provide access to technical expertise and experimentation in the area of semiconductors, helping companies,

<sup>1</sup> Refer to Annex IV for further information on the application of this article.

SMEs in particular, to approach and improve design capabilities and developing skills. Competence centres will provide services to semiconductor stakeholders, especially targeting start-ups and SMEs. Examples include facilitating access to pilot lines and to the European virtual design platform, providing training and skills development, support to finding investors, making use of existing local competencies or reaching out to relevant vertical sectors. The services should be provided on an open, transparent and non-discriminatory basis. Each competence centre should connect and be part of the European network of competence centres in semiconductors and should act as an access point to other nodes of the network.

#### 2.1.2. Expected outcomes

The competence centres shall

- o **promote the actions** developed by the Chips JU in the frame of the Chips for Europe Initiative as well as the success stories.

- o be a **first entry point for** users (mainly SMEs and startups) and guide users in accessing the other infrastructures set up by the Chips JU under the Initiative: the design platform and the pilot lines.

- o be essential in facilitating skill development activities.

- o support companies in accessing the Chips Fund.

- O Perform other activities that can help European organizations (mainly SMEs and startups) to develop their activities in the frame of the Chips for Europe initiative and vice versa support the consortia that implement the pilot lines and the design platform to reach out to the larger community of organizations that could profit from those efforts.

#### **2.1.3.** Scope

Chips CCs should have a **specialised area of expertise**. Each competence centre decides on its specialisation in a certain technology, domain, or set of activities. It should be reflecting the specialisation of the stakeholders of that area / Participating State and should push innovation in that area within the Union. Examples of areas of expertise are Chips for medical devices, power electronics, cutting-edge semiconductors, heterogeneous integration, packaging, metrology, EDA simulation tools, Chips for automotive, silicon photonics and photonic integrated circuits, quantum Chips, system design, etc.

Chips CCs shall offer several **support activities**. Offering such support activities is common to all Chips CCs and is a necessary characteristic to belong to the network of competence centres. Support activities can be:

- Awareness raising, promoting services, promoting success stories: the services offered by Chips CCs may be new and may not be well recognised in the beginning. Therefore, Chips CCs need to raise awareness about their services, need to promote their services, and may need to develop an outreach program to promote the Chips CC services to potential user companies, esp. smaller enterprises. Chips CCs may need to go to many events in their countries to increase familiarity of their services with their target customers. They may need to target specific vertical sectors. They may need to promote success stories that show how their services benefit their customers. They may need to hire staff with the right soft skills to interact with customers and provide the interface between technical Chips CC staff and customers.

- Facilitate access to the design platform and to pilot lines by providing information and support on how to access the platform or the pilot lines when users do not have the knowledge or expertise to do so directly.

- Support interested users in developing semiconductor solutions (technology transfer) by supporting technology transfer activities at local/regional/national level and where needed at EU level. Research activities as well as operation, administration or procurement of infrastructures are not within the scope of Chips CCs, but competence centres are expected to advise on such activities and support knowledge transfer e.g. from relevant R&I initiatives to the local semiconductor ecosystem. Support could also be in the form of matchmaking between a research organization and a user.

- In addition, Chips CCs could grant facilitated access to experts in such areas as legal compliance and business development. They may offer assistance to SMEs in creating business plans and conducting market studies.

- Providing (access to) training on skills: Advanced training on specific design and manufacturing skills and practices is often difficult to access for SMEs and other stakeholders. They need access to education services for development of skills in different disciplines but also for different audiences or levels (e.g. bachelor, masters level), access to top-level teachers, or support for the set-up of a credentials/microcredentials framework. Chips CCs should support local and national training and skills development in the area of semiconductor technologies through face-to-face as well as online training (e.g. via MOOC platforms). Chips CCs should determine what is needed in their countries, should know the competences of other Chips CCs, and where

needed – provide trainings to other CCs ('train-the-trainer'). Trainings can be provided by CCs themselves, or by third parties hired by the centres. A variety of training models can be used, ranging from alternation model or cluster model, via on-the-job trainings and apprenticeships, to crash courses and mentoring programmes.

- Participate in the organization of a European Network of Chips Competence Centres (ENCCC) and facilitate the access to this network. Part of the resources of a Chips CC should be dedicated to building and extending this network, in collaboration with a Coordination and Support Action (see Chips-CCC-2: Support to the European Network of Chips Competence Centres). Chips CCs should help stakeholders, especially smaller companies such as SMEs and start-ups, to connect to other competence centres within the overall network of competence centres. They should provide stakeholders with information on relevant competences in the network as well as on national and international programs, companies, and research centres in semiconductors. A Chips CC should help a stakeholder to connect to the right competence centres within the overall network of competence centres, if the local/national Chips CC does not have the right competences to support the stakeholder. In return, a Chips CC will support stakeholders from other regions and countries that need its (specialised) expertise through the network of competence centres.

- Chips CC should act as entry points to other European initiatives, such as the network of European Digital Innovation Hubs, HPC competence centres, cybersecurity centres, etc. The goal is to ensure that national stakeholders have access to the best available expertise and support in Europe, by matching stakeholders' needs with the available expertise in the network of competence centres. Such expertise may be the specialisation of another competence centre and be accessible through the ENCCC.

- Promoting the Chips Fund and facilitating access to venture capital: SMEs and startups are often faced with insufficient financial support and have difficulties to get loans, equity, and/or grants. In particular, startups experience difficulties in managing resources and investment at the initial stage. Competence centres in semiconductors may support SMEs, startups, and other companies to access the Chips Fund. They may also support companies in finding investors, including venture capital.

- Awareness raising, promoting services, promoting success stories: the services offered by Chips CCs may be new and may not be well recognised in the beginning. Therefore, Chips CCs need to raise awareness about their services, need to promote their services, and may need to develop an outreach program to promote the Chips CC services to potential user companies, esp. smaller enterprises. Chips CCs may need to go to many events in their countries to increase familiarity of their services with their

target customers. They may need to target specific vertical sectors. They may need to promote success stories that show how their services benefit their customers. They may need to hire staff with the right soft skills to interact with customers and provide the interface between technical Chips CC staff and customers.

Chips CCs should primarily offer services that address the needs from their prime user communities. Nevertheless, Chips CCs should also answer the needs from other organisations, e.g. from other countries, and work in close coordination and collaboration with the rest of the Network to achieve the highest possible impact, ensure the most efficient use of the CCs' resources, and to avoid duplication of efforts among the Chips CCs and with other initiatives, such as the European Digital Innovation Hubs.

## 2.1.4. Access to the Chips CC

Access to a Chips CC's services shall be open to several users and be granted on an **open**, **transparent and non-discriminatory basis**.

In line with the Chips Act, services to SMEs or public sector organisations (e.g., RTOs) could be made available **for free or against reduced prices**, and **against market prices for large companies**. Given that large enterprises need to pay the market price, they will not be considered as beneficiaries of State aid. Conversely, public entities involved in <u>non-economic activities</u> or exercising public authorities' functions can benefit from access granted at reduced fees or for free, as such activities are not subject to State aid control. However, public entities (and also research organisations) when involved in <u>economic activities</u>, follow the same rules as applicable to large undertakings vs SMEs, i.e. they need to pay the full market price (large undertakings) or get access at reduced fees or for free (SMEs).

As a consequence, every competence centre must, in their proposal, draw up an **indicative price list for all their services, based on market prices**. The **reduction of prices** for SMEs or other eligible entities has to be made public as well, similarly to the prices charged on market terms by the competence centres. Proposals must include the methods to calculate the market price used in the price list and/or the cost of the services, so that external experts can evaluate its validity and appropriateness.

Moreover, services provided should be accessible in the national languages as well as in English.

The Chips CCs must be established as organisations with appropriate visibility to national, regional and local communities. In general, Chips CCs should employ semiconductor specialists, primarily with full-time contracts, and with expertise in areas that are most relevant for the national communities and the specialisation of their centres. A Chips CC should have an independent organisational structure and its staff should not work under external supervision.

#### 2.1.5. Consortia for CC

A Chips CC is a **single organisation** or a **coordinated group** of organisations (consortium) with complementary expertise, established with a **non-profit objective**, aiming to promote the use of semiconductor technologies. In the case of a consortium, one organization will be appointed as coordinator. Although there is formally no limit on the number of entities setting up a competence centre, a small number of partners per Chips CC is desirable. There is no obligation for a group of organisations to create a dedicated legal entity. A Chips CC can be built on established entities in the field or can be set up from scratch.

As a matter of example, Research and Technology Organisations (RTOs) and universities could become a national competence centre of a Participating State in semiconductors. Enterprises may also set up a competence centre, or be part of a group establishing a competence centre. However, the centre must have a non-profit objective and services must be offered not-for-profit.

Candidates for competence centres are not limited to those legal entities that are involved in the set-up of pilot lines, the design platform, or are somehow involved in any other way in the Chips for Europe Initiative. Being involved in the setup and/or operation of infrastructures is not a requirement for competence centres. The Participating States have the sole and direct responsibility to propose candidate competence centres.

The Chips for Europe Initiative will support the establishment of competence centres throughout the Union and Participating States. The European Network of competence centres in semiconductors may comprise zero, one, or more centres per eligible country (Participating States). Participating States may decide to team up with other countries and support cross-border competence centres.

Typical **users** of the services offered by a Chips CC are companies, in particular local/national SMEs and startups, RTOs, and academic institutions at the regional, national and EU level.

Public authorities and large enterprises may also use the services of a competence centre, but normally they are not the prime customers.

#### 2.1.6. Size, funding and access to services

The call will be implemented as a single DEP call with open access. As a result of the evaluation of the call, selected consortia will be offered to sign a DEP grant.

The Union will make available up to EUR 1 million per year, per country, for a 4-year period. There is no differentiation based on country size, i.e. all countries may get the same maximum amount of EU funding per year to support their competence centres. There is also no differentiation based on the number of competence centres that a country wants to support, i.e. the maximum, annual amount of EU funding may be used to support one or more competence centres.

Participating States are expected to **co-finance** their national competence centres together with the Union, i.e. 50% will be funded through EU contributions and 50% through national contributions. Union funding is conditional on the availability of the same (or higher) amount of national contributions. Participating States may provide the same amount of maximum annual, financial contributions as the Union, i.e. EUR 1 million per year. Participating States may also opt to provide a higher amount of annual national contributions (i.e. higher than EUR 1 million per year), but this will <u>not</u> lead to a similar, higher annual Union contribution. Participating States may provide a lower amount of annual national contributions (i.e. lower than EUR 1 million per year), and this will lead to a similar, lower annual Union contribution.

The EU funding for the competence centres will be made available through Digital Europe grants, which allow to fund **specific cost items**:

- Qualified personnel of the competence centre to deliver the services mentioned above to the organisations participating in a CC, including subcontracting for specialists;

- Procurement and/or depreciation costs for equipment and facilities, both hardware and software;

- Travel grants for personnel of the competence centre and local stakeholders to carry out their activities.

- Indirect costs are included as 7% of the direct cost.

## 2.1.7. Type of Action

DIGITAL Simple Grants – 50% **maximum** EU funding rate

#### 2.1.8. Admissibility

Admissibility conditions are described in Annex II "General DIGITAL conditions" of this document.

#### Regarding page limits:

- The page limit for the chapter RELEVANCE is 20 pages

- The page limit for the chapter IMPLEMENTATION is 60 pages

- The page limit for the chapter IMPACT is 20 pages

#### **2.1.9.** Eligibility and selection process

Applications will only be considered eligible if their content corresponds wholly (or at least in part) to the topic description for which they are submitted.

Participant eligibility conditions are described in Annex II "General DIGITAL conditions" of this document.

Candidates to the consortium for a Chips CC must at least fulfil the following criteria:

- Appropriate competences to provide the services outlined above;

- Appropriate management capacity, staff and infrastructure necessary to provide the services outlined above;

- Operational and legal means to apply the administrative, contractual and financial management rules that come with a grant agreement;

- Appropriate financial viability, corresponding to the level of funds they will be called upon to manage.

The Chips JU will launch an **open call for proposals** to set up competence centres in semiconductors. To be eligible, a proposal submitted to the call will have to provide proof that the centre has been designated by its Participating State and that it will be co-financed by the Participating State. In particular, **the proposal shall include as mandatory document a letter**

**describing the formal commitment of the Participating State,** as the one provided in Annex I to the present document.

In the **evaluation phase**, the Chips Joint Undertaking will evaluate proposals by designated candidate centres. In case a Participating State has designated more candidates than its desired number and size of competence centres, the evaluation will be competitive. Otherwise, the evaluation will be a quality assessment of designated candidates.

Eligible proposals will be evaluated according to the criteria of DEP (see Award criteria) and all those scoring above all thresholds will be ranked. Based on the ranked list, the Chips JU's Public Authorities Board will select proposals for funding. Selected proposals will get a grant from the Chips JU for a duration of 4 years.

Further details on the evaluation procedure are described in the Governing Board Decision on the evaluation and selection procedures related to the calls launched by the Chips  $JU^2$

#### 2.1.10. Financial and operational capacity and exclusion

Please refer to Annex II "General DIGITAL conditions" of this document.

#### 2.1.11. Award criteria used for open calls

The award criteria used are as follows:

#### Criterion 1 - Relevance

- Alignment with the objectives and activities as described in section 2.1 of the Chips JU Work Programme 2023-2027- Appendix 4.

- Contribution to long-term policy objectives, relevant policies and strategies, and synergies with activities at European and national level;

## Criterion 2 - Implementation

- Maturity of the proposed CC;

- Soundness of the implementation plan and efficient use of resources;

<sup>2</sup> Decision GB 2024.71

• Capacity of the applicants, and when applicable the consortium as a whole, to carry out the proposed work.

## Criterion 3 - Impact

- Extent to which the project will achieve the expected outcomes and deliverables referred to in the call for proposals and, where relevant, the plans to disseminate and communicate project achievements;

- Extent to which the project will strengthen competitiveness and bring important benefits for society;

**2.1.12. Score**The scores will be given with a resolution of one decimal.

| <u>Criteria</u> | Range       | Weight (**) | Threshold (*) |

|-----------------|-------------|-------------|---------------|

| Relevance       | <u>0-5</u>  | <u>1</u>    | <u>3</u>      |

| Implementation  | <u>0-5</u>  | <u>1</u>    | <u>3</u>      |

| Impact          | <u>0-5</u>  | <u>1</u>    | <u>3</u>      |

| Total           | <u>0-15</u> |             | <u>10</u>     |

<sup>(\*)</sup> threshold applies to unweighted score.

<sup>(\*\*)</sup> the weight is only used to establish the ranking of the proposals.

## 2.2. Chips-2024-CCC-2: Support to the European Network of Chips Competence Centres

| Chips-2024-CCC-2                 |                                                                                            |  |

|----------------------------------|--------------------------------------------------------------------------------------------|--|

| DIGITAL-Chips-2024-CSA-CCC-2     | EU Expenditure = Max. EURO 4 Mio                                                           |  |

| Instrument / Type of Action      | Coordination and Support Action (DEP)                                                      |  |

| Security                         | Call restricted on the basis of Article 12(6) of the Regulation (EU) 2021/694 <sup>3</sup> |  |

| Publication date                 | 04th Jul 2024                                                                              |  |

| Deadline Submission of proposals | 2 <sup>nd</sup> Oct. 2024 at 17:00 Brussels Time                                           |  |

## **2.2.1. Expected Outcomes**

The European semiconductor ecosystem will be strengthened through an effective network of Chips Competence Centres (Chips CCs) supporting the adoption and use of semiconductor technologies, in particular by SMEs, and taking into account the specific needs of the local, regional and/or national ecosystem(s). The coordinated network will facilitate access to pilot lines and the European virtual design platform and knowledge transfer within the Chips CCs. The Coordination and Support Action will ensure the European network of Chips Competence Centres will be embedded in the European semiconductor ecosystem with strong links to other European initiatives, for example, in the area of training.

Moreover, the action will result in

- Effective coordination and exchange of best practices and information among the network of Chips CCs;

- Facilitated access to services and training offered at national or regional level to interested Chips CCs and other potential users (from industry, academia or public sector);

- Maximised visibility and outreach of Chips CCs, in particular to SMEs and industry;

- Improved coordination and increased availability of training activities on semiconductor technologies across Chips CCs and within the European semiconductor ecosystem;

The main objective of the Coordination and Support Action is to maximize networking between existing European points of semiconductor knowledge and expertise. The tasks and services will provide a single focal point at European level, which will be responsible for the support of the Chips Competence Centres, the exchange of best practices among these centres, facilitating the sharing of knowledge and information, networking and training across competence centres.

-

<sup>3</sup> Refer to Annex IV for further information on the application of this article.

In order to accomplish these objectives, the selected consortium should also establish effective cooperation with other European initiatives, in particular regarding skills and training in semiconductors.

## **2.2.2.** Scope

Proposals should aim at supporting the networking among the Chips Competence Centres. In particular, it is expected to establish a communication platform, facilitate dialogue, promote the objectives of the Centres, and organize outreach events and workshops. The activities should leverage on synergies and complementarity of the centres.

The Coordination and Support Action should:

- Support the exchange of best practices among Chips CCs;

- Disseminate the activities of the Network. Maximise visibility and outreach of Chips CCs, in particular to SMEs, industry and the public sector;

- Promote the services of the Chips CCs, specifically addressing the needs of SMEs;

- Attract new users and support the engagement of industry and SMEs in the activities of the Chips CCs;

- Educate and assist Chips CCs in technology transfer practices, including IP management, where relevant;

- Define and monitor meaningful qualitative and quantitative KPIs for the European Network of Chips Competence Centres and for the Centres;

- Maintain an overview of specific specialisations and competence of the various Centres;

- Support matchmaking for specific competences;

- Facilitate access to services and training offered at national level to interested Chips CCs and other potential users;

- Support the organisation of community building events for users and Centres sharing similar interests;

- Support the connection of Chips CCs to relevant other initiatives, in particular to initiatives on skills and workforce development;

- Act as the first online point of contact for all information related to the Chips Competence Centres.

## 2.2.3. Type of Action

DIGITAL Coordination and Support Actions – 100% EU funding rate

#### 2.2.4. Admissibility

Admissibility conditions are described in Annex II "General DIGITAL conditions" of this document.

Regarding page limits:

- The page limit for the chapter RELEVANCE is 20 pages

- The page limit for the chapter IMPLEMENTATION is 60 pages

- The page limit for the chapter IMPACT is 20 pages

## 2.2.5. Eligibility

Applications will only be considered eligible if their content corresponds wholly (or at least in part) to the topic description for which they are submitted.

Participant eligibility conditions are described in Annex II "General DIGITAL conditions" of this document.

#### 2.2.6. Financial and operational capacity and exclusion

Please refer to Annex II "General DIGITAL conditions" of this document.

#### 2.2.7. Evaluation procedure

Please refer to the Governing Board Decision on the evaluation and selection procedures related to the calls launched by the Chips JU<sup>4</sup>.

#### 2.2.8. Award criteria

The award criteria used are as follows:

<sup>4</sup> Decision GB 2024.71

#### Criterion 1 - Relevance

- Alignment with the objectives and activities as described in section 2.2 of the Chips JU Work Programme 2023-2027- Appendix 4.

- Contribution to long-term policy objectives, relevant policies and strategies, and synergies with activities at European and national level;

## Criterion 2 - Implementation

- Maturity of the project;

- Soundness of the implementation plan and efficient use of resources;

- Capacity of the applicants, and when applicable the consortium as a whole, to carry out the proposed work.

#### Criterion 3 - Impact

- Extent to which the project will achieve the expected outcomes and deliverables referred to in the call for proposals and, where relevant, the plans to disseminate and communicate project achievements;

- Extent to which the project will strengthen competitiveness and bring important benefits for society;

#### **2.2.9.** Score

The scores will be given with a resolution of one decimal.

| <u>Criteria</u> | Range       | Weight (**) | Threshold (*) |

|-----------------|-------------|-------------|---------------|

| Relevance       | <u>0-5</u>  | <u>1</u>    | <u>3</u>      |

| Implementation  | <u>0-5</u>  | <u>1</u>    | <u>3</u>      |

| Impact          | <u>0-5</u>  | <u>1</u>    | <u>3</u>      |

| Total           | <u>0-15</u> |             | <u>10</u>     |

<sup>(\*)</sup> threshold applies to unweighted score

<sup>(\*\*)</sup> the weight is only used to establish the ranking of the proposals

## 2.3. Chips-2024-CPL-5: Pilot Line on Advanced Photonic Integrated Circuits

| Chips-CPL-5                                                                                                                                         |                                                                                            |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| Max EU Expenditure                                                                                                                                  | Max. EURO 185 Mio                                                                          |  |

| <ul> <li>Call for Expression of Interest<br/>DIGITAL-Chips-2024-CfEoI-CPL-5</li> <li>Setup, integration<br/>HORIZON-Chips-2024-RIA-CPL-5</li> </ul> | Indicative EURO 105 Mio; Max EURO 150 Mio Indicative EURO 60 Mio; Max EURO 100 Mio         |  |

| Operational                                                                                                                                         | Indicative EURO 20 Mio; Max EURO 40 Mio                                                    |  |

| DIGITAL-Chips-2024-SG-CPL-5                                                                                                                         |                                                                                            |  |

| Mode                                                                                                                                                | Call for Pilot Line (CPL)                                                                  |  |

| Security (for DIGITAL calls only)                                                                                                                   | Call restricted on the basis of Article 12(6) of the Regulation (EU) 2021/694 <sup>5</sup> |  |

| Publication date                                                                                                                                    | 25 <sup>th</sup> July 2024                                                                 |  |

| Deadline Submission of proposals                                                                                                                    | 17th September 2024 at 17:00 Brussels Time                                                 |  |

#### **2.3.1.** Context

The digital transformation and the shift towards more sustainable energy solutions have led to a profound change in the technological demands of various industries, from telecommunications to healthcare and automotive sectors. Traditional electronic circuits, primarily based on silicon, are reaching their physical and operational limits, especially in terms of efficiency, speed, and miniaturization. This challenge is magnified by the increasing complexity of applications such as 5G/6G communications, autonomous driving, and pervasive AI technologies, which demand rapid processing and transmission of vast amounts of data with minimal latency and power consumption.

Photonic Integrated Circuits (PICs), which leverage light to process and transmit information, emerge as a transformative solution to these challenges. Unlike their electronic counterparts, PICs offer the potential for higher bandwidth, faster speeds, and lower energy consumption, making them ideal for the next generation of high-performance computing systems, advanced sensor arrays, and ultra-fast communication networks. The integration of PICs with Electronic Integrated Circuits presents a compelling synergy that can address critical bottlenecks in electronic systems, particularly in data centres and cloud computing infrastructures where energy efficiency and processing speed are paramount.

Europe stands at a juncture in the field of integrated photonics. While it has established a robust foundation in photonics research and industrial applications, the region faces intense global competition, notably from North America and Asia, where significant investments are being

\_

<sup>5</sup> Refer to Annex IV for further information on the application of this article.

funnelled into the development of advanced PIC technologies. Europe's technological sovereignty and competitiveness in global markets increasingly hinge on its ability to innovate and maintain leadership in the emerging sector of photonic technologies.

To address these challenges and opportunities, there is a pressing need to establish a dedicated pilot line for Photonic Integrated Circuits within Europe. This initiative will focus on advancing PIC technologies beyond the current state-of-the-art, particularly extending operational wavelengths from the near-infrared into the visible and mid-infrared spectrums. This expansion is crucial for tapping into new application areas such as biomedical imaging, quantum computing, and environmental sensing, which require specific wavelengths for optimal performance.

The proposed pilot line needs to serve as a critical infrastructure for bridging the gap between laboratory research and industrial-scale production, facilitating the development of reliable, scalable, and cost-effective PIC solutions. It should foster collaboration among research institutions, SMEs, and large corporations across Europe, driving innovation, and accelerating the commercialization of PIC technologies. By doing so, it should not only enhance Europe's competitive edge in a key technological domain but also contribute significantly to the continent's economic resilience and strategic autonomy in critical technologies.

#### 2.3.2. Expected Outcomes

The proposed pilot line shall be established with all the necessary equipment, facilities, and needs to target the following main **objectives**:

- **Develop and enhance PIC technologies** by extending the operational wavelengths into the visible and mid-infrared spectrum, crucial for applications such as lidar and advanced sensing.

- **Develop scalable and cost-effective manufacturing processes** for PICs, ensuring compatibility with current industrial standards and promoting widespread adoption.

- **Foster the integration of PICs** with electronic integrated circuits, enhancing the functionality and efficiency of combined systems for applications in computing, telecommunications, and beyond.

- **Innovate in** the fields of photonic **testing and packaging** to improve reliability, scalability, and performance of PICs.

- **Enable rapid prototyping** through Multi-Project Wafer runs, allowing for timely validation and iteration of PIC designs.

- **Develop demonstrators** to validate the achievement of the advanced PICs technology and to quantify its performance.

## Expected Results of the Pilot Line:

The **expected results** for this pilot line should therefore comprise:

- A sustainable pilot line open to all European stakeholders, especially focusing on enabling SMEs and start-ups to leverage advanced PIC technologies.

- Process Design Kits and Assembly Design Kits, crucial for the design and development of next-generation PICs.

- Extended capabilities of current PIC technologies to larger wafer sizes and integrate built-in self-test methodologies, enhancing the performance and integration of PIC modules.

- Creation of **intellectual property**, boosting European production capacities in PIC technologies.

- Fostered collaborative development through **synergies with other Chips JU pilot lines**, enhancing the overall innovation capacity and technological leadership of Europe in semiconductor technologies, ensuring complementarity especially with the pilot lines dedicated to quantum technologies, heterogeneous integration, and wide bandgap materials.

- Comprehensive **training programs and skill development initiatives** to ensure that European technologists and engineers are equipped with the knowledge and tools necessary to excel in the field of photonic integration.

#### **2.3.3.** Scope

The proposed pilot line should work at all levels of the main technological steps:

- The development of advanced PIC modules to enhance performance capabilities in existing systems and address the high demand for faster data processing and communication. This will involve improving light source technology, detector efficiency, and modulator capabilities, particularly extending into the visible and mid-infrared spectrums. The modules will align with the latest industry standards and are expected to play a crucial role in applications ranging from telecommunications to advanced sensing and biophotonics.

- **Refinement of the fabrication processes** will be fundamental to support the production of PICs. The pilot line should optimize the lithography, etching, and deposition processes that allow for the scaling down and increased yield of photonic features.

- **Multi-Project Wafer** runs will be instrumental in the prototyping phase, offering a cost-effective route for validating and iterating PIC designs. These runs will support a variety of projects from a broad user base, including academia, research

institutions, and industry partners according to an operational and access policy defined or the collaboration with those stakeholders.

It should give open access to various PIC technology platforms, including III-V, Si, SiNx and hybrid-integration.

As part of its commitment to fostering an innovative and collaborative environment, the pilot line should **continuously deliver updated Process Design Kits** that reflect the advancements in PIC technologies. The access policy from the different stakeholders to the pilot line should be defined in the proposal according to fair and non-discriminatory principles.

The pilot line should also serve as a training ground, with the hosting entity and other partners providing necessary **training to European partners**. The training initiatives will also be directed toward students and professionals for up-skilling and re-skilling, with the goal of attracting and nurturing new talents within the European semiconductor industry.

Finally, the pilot line should promote the **collaboration** with other pilot lines, with design platforms and competence centres to enable contributions from stakeholders that develop specialized expertise in areas relevant to this pilot line's focus.

A Call for Pilot Line includes three interrelated calls:

- Call for Expression of Interest for the selection of a Hosting Consortium

- Call for proposals for Set-up, integration and process development, funded under the Horizon Europe Programme

- Call for proposals for the operational activities of the pilot line, funded under the Digital Europe Programme

The evaluation of a CPL will consist of the evaluation of the three interrelated calls.

This document describes the details of the call: topic description and the budgets as well as the procedures for evaluation and selection.

#### 2.3.4. Specific provisions applicable to Calls for pilot lines.

The following points on access conditions, Intellectual Property, and co-ownership apply to all Calls for pilot lines. More detailed provisions are stated in the Call for Pilot Line part of this document; in case of conflicts, those provisions prevail over the provisions stated here.

#### 2.3.4.1.Access conditions for pilot lines

Expressions of Interest submitted to the calls below need to take into account the following access conditions:

- Access to a pilot line needs to be open to a wide range of public and private users across the Union and granted on a transparent and non-discriminatory basis directly proportional to the financial contribution by the Union to the total costs of those activities.

- Access needs to be provided on market terms, or on a cost-plus-reasonable-margin basis for large undertakings, while granting preferential access or reduced prices for academic institutions, start-ups and SMEs.

- PDKs/ADKs need to be accessible for different categories of users (academia, research, industry etc.) and will be required to be available via the European virtual Design Platform.

- Access conditions for non-EU organisations need to take into account the Union's commitments to international cooperation under its strategic partnerships with like-minded countries.

Access to the pilot lines should be based on fair and non-discriminatory principles and should be limited to Participating States of the Chips JU, meaning EU Member States, EEA countries and those countries that have been associated to Horizon Europe or Digital Europe Strategic Objective 6, under which the pilot lines are funded. In determining access to the pilot lines for users established in any Participating State but controlled from third countries that are not Participating States of the Chips JU, consortia must take into consideration the following two main criteria:

- EU added value, i.e., their contribution to the objectives of the Chips Act as set out in Article 4.

- Economic security considerations.

The above access criteria should also be duly considering other relevant provisions of the Chips Act Regulation (notably Recital 11, and Recital 27), such as for example those in relation to the handling of sensitive information, potential risks of infringement of intellectual property (IP) rights, unauthorised disclosure of trade secrets and IP rights, security, confidentiality, or the leakage of sensitive emerging technologies within the semiconductor sector.

Only users from organisations that can clearly demonstrate their contribution to EU added value, their alignment with European economic security shall be granted access. Users from third countries will be granted access when this is foreseen in the international obligations of the Union concerning semiconductors, as these defined in any relevant Digital Partnerships or Trade and Technology Council agreements. In this case, such users should still commit to fulfil the above access criteria.

Selected consortia will be tasked to further elaborate on the above access criteria as well as access conditions and widely publish them. Such access conditions shall duly take into consideration the following elements: security procedures (both for physical and digital), cybersecurity protection of digital systems used to operate the pilot line, access control to facility and digital systems (including logging of access), security clearance, setup of different restricted areas with different security levels (such as the compartmentalisation of both digital and physical infrastructures).

#### 2.3.4.2.Intellectual Property

Expressions of Interest submitted to this call need to take into account the following provisions on Intellectual Property:

- Intellectual Property provisions must comply with standard Horizon Europe and Digital Europe rules. For instance, IPR transfers to legal entities outside the EU will be subject to approval by the granting authority.

- However, any transfer of IP rights from the hosting consortium to any third parties needs to be tied to either potential investment in Europe or an international agreement.

- Possible conditions for non-exclusive licensing of IP need to be considered.

- Consortia are invited to further reflect on the impact of EU co-ownership on IP policy.

#### 2.3.4.3.Co-ownership

The ownership share of the Chips Joint Undertaking of the acquired equipment infrastructure in a pilot line is 50%.

#### 2.3.5. Other general provisions

#### 1. Gender dimension

The integration of the gender dimension (sex and gender analysis) in research and innovation content is not a mandatory requirement. However, activities concerning user interaction or sensing (e.g. of medical devices, consumer goods, cars with automatic driving features, ...) need to include (if relevant) considerations of how the gender dimension affects system design, and hence whether it affects the technical specifications.

#### 2. Financial capacity.

In line with the Financial Regulation, coordinators will be invited to complete a self-assessment using an on-line tool.

#### 3. Consortium agreement:

Participants are required to conclude a consortium agreement. For the partners of a Participating State that coordinates grants, specific rules may apply regarding the eligibility to national funding.

#### 4. Costs for the pilot line:

can be introduced as of the day after the publication date of the Call for Pilot Line.

## 2.4. Chips-2024-CDP-1: Design platform

| Chips-2024-CDP-1                                                                     |                                                                                            |  |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| Max EU Expenditure                                                                   |                                                                                            |  |

| <ul> <li>Call for Expression of Interest</li> </ul>                                  | EURO 0                                                                                     |  |

| DIGITAL-Chips-2024-CfEoI -CDP-1                                                      |                                                                                            |  |

| <ul> <li>Coordination and Support Action<br/>DIGITAL-Chips-2024-CSA-CDP-1</li> </ul> | Max. EURO 25 Mio                                                                           |  |

| Mode                                                                                 | Call for Design Platform.                                                                  |  |

| Publication date                                                                     | 4 <sup>th</sup> Jul 2024                                                                   |  |

| Opening date                                                                         | 12th Aug 2024                                                                              |  |

| Security                                                                             | Call restricted on the basis of Article 12(6) of the Regulation (EU) 2021/694 <sup>6</sup> |  |

| Deadline Submission of proposals                                                     | 10th Oct 2024 at 17:00 Brussels Time                                                       |  |

#### **2.4.1.** Context

Semiconductor circuit design is the process of creating integrated circuits (ICs) and system-on-chips (SoCs) by defining the functionalities and characteristics of chips, capturing a substantial portion of the added value within the semiconductor value chain. The trend is moving towards more complex, application-specific, highly integrated semiconductors, making cutting-edge design crucial for competitiveness and differentiation in a wide range of applications. In this context, fabless companies are well-positioned to drive technological advancements and meet the needs of diverse applications, reinforcing their pivotal role and growth in the semiconductor industry.<sup>7</sup>

The Chips Act underscores the strategic importance of fostering chip design growth in Europe to enhance the competitiveness of the Union's semiconductor industry. Pillar I of the Chips Act, the Chips for Europe Initiative, outlines an ambitious plan to strengthen the Union's resilience in semiconductor technologies, including promoting the growth of fabless companies focused on leading-edge technologies. This is especially pertinent given that the European share of global fabless semiconductor companies' revenues has shrunk to critically low levels (currently around 1%), highlighting the urgent need for strategic initiatives to bolster this sector and enhance Europe's competitiveness. A critical mass of fabless companies is also key to generate further demand that would justify increased investment in semiconductor manufacturing capacity in Europe.

<sup>6</sup> Refer to Annex IV for further information on the application of this article.

<sup>7</sup> A fabless company is a company that designs and markets hardware devices and semiconductor chips but outsources the fabrication (manufacturing) of those devices to a specialised semiconductor fabrication plant, or 'fab'.

Recognising the Union's limited fabless capacity, and the significant barriers to entry in chip design, the Design Platform shall focus on nurturing emerging companies in the sector. The Design Platform is at the heart of the Chips for Europe Initiative, it is envisaged as a key instrument to foster the development of a strong design ecosystem in the Union, by creating a pipeline of highly innovative European fabless companies, focusing particularly on the growth of start-ups and SMEs.

At the core of the design process lie a series of Electronic Design Automation (EDA) tools, Intellectual Property (IP) blocks and Process Design Kits (PDKs) including standard cell libraries. This is coupled with either on-premises or cloud-based computing resources. Each of these elements requires a separate acquisition process for the designer, often involving very significant costs and its own complex procedures.

This activity aims at building a pioneering cloud-enabled European Design Platform that will aid users, particularly start-ups and SMEs, in accessing a wide range of advanced tools, assets and services to develop their chips. The platform, by amalgamating these resources, shall support users along the innovation process, in preparation for industrial deployment. It will facilitate increased opportunities for innovation across the industry by lowering the barrier of entry for chip design in Europe, enabling both small and large entities to drive technological progress, thereby strengthening EU's position in the global semiconductor market. To this end, the Design Platform shall encompass a combination of a cloud-based infrastructure together with a number of dedicated design and other relevant services and activities, that are elaborated on further below.

The primary objectives of the platform are to cultivate a robust chip-design ecosystem in Europe and to ensure that start-ups and SMEs have access to top-tier tools and support services comparable to those more easily accessible to large enterprises. This platform, as a unified European infrastructure combined with comprehensive user support services, aims to democratise chip design in Europe by facilitating access, for all eligible users, to advanced tools and resources, irrespective of their size.

The main target users of the Design Platform shall be commercial entities, particularly start-ups and SMEs, for the purpose of pre-competitive activities such as research, development and innovation up to experimentation and tape-out. Such entities are then expected to engage in regular commercial contractual agreement with Electronic Design and Automation tool vendors outside of the Design Platform upon maturity. Complementary support to that already provided by EUROPRACTICE for academia and research institutes can be considered.

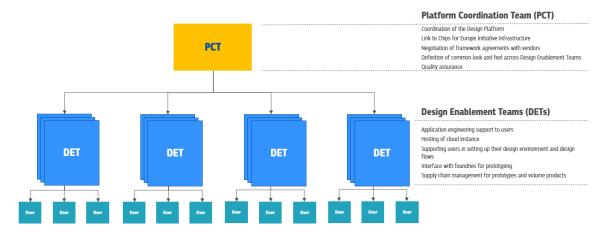

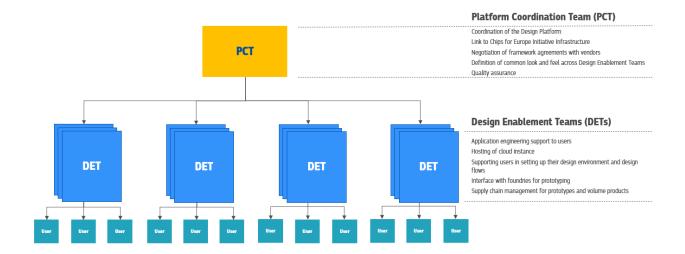

This call concerns the selection of the consortium in charge of the overall coordination of the Design Platform, referred to as the Platform Coordination Team (PCT), which shall serve as the **hosting entity** for the Design Platform's virtual infrastructure and central services, coordinating access to a wide range of tools, assets and services.

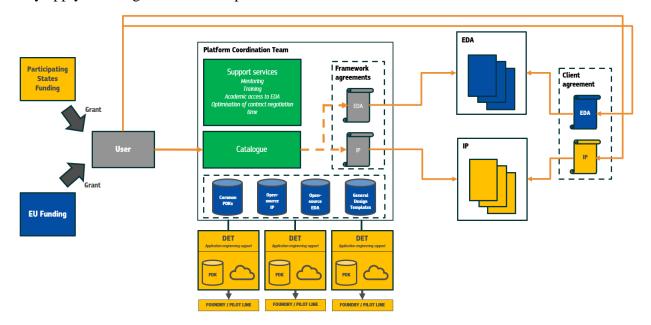

The chosen implementation model foresees a central consortium, referred to as the *Platform Coordination Team (PCT)* that operates the overall Design Platform initiative, serves as the hosting entity of the central cloud infrastructure and manages the development of its users. The PCT shall assist the Chips Joint Undertaking (Chips JU) in defining the technical specifications

of the cloud service for the platform to be procured by the Chips JU through a dedicated *Call for Tenders*. Following the procurement procedure, the PCT shall manage on behalf of the Chips JU the formal test, validation and delivery of the cloud-enabled platform and its integration in the broader Design Platform initiative. This shall be done in close cooperation with a selected service provider following the *Call for Tenders* for the procurement of the cloud service mentioned above. The PCT shall also be responsible for the further development and operationalisation of the Design Platform, in close cooperation with the selected service provider. It shall also be responsible for coordinating training, EDA tool and IP licensing support and the coordination of decentralised teams referred to as *Design Enablement Teams* (*DETs*). The selection of a consortium operating as the PCT is the purpose of this call.

The PCT will be complemented by a number of DETs that shall set-up a cloud-based environment for users designing on the platform, support them in their design cycle and facilitate access of users to foundry services. The PCT shall provide the set of requirements that DETs must fulfil in order to apply for integration in the cloud-based platform. A call for the DETs shall follow at a later stage.<sup>8</sup>

The Design Platform shall complement the ongoing EUROPRACTICE initiative, currently financed by the Chips JU project RETICLES. While EUROPRACTICE currently addresses the needs of academia, the Design Platform, in its first iterations shall target commercial enterprises, particularly start-ups and SMEs. Eventually, it is anticipated that in the future EUROPRACTICE's services may be integrated into the Design Platform.

#### 2.4.2. Expected outcomes

The main expected outcome of this initiative is the development of a robust chip design ecosystem in Europe. Furthermore, the consortium acting in the role of the PCT is expected to contribute to the following outcomes:

- Easy cloud-enabled access to electronic design tools (including proprietary and opensource tools), libraries of design templates, as well as training and support services, available through an inclusive design platform, accelerating chip design and reducing time-to-market for users.

- The cloud services, procured by the Chips JU, may be developed and maintained by third parties, however the PCT, in line with a Hosting Agreement, shall assume responsibility for the coordination and execution of the various related activities and services described below.

- The PCT shall oversee that the cloud service procured by the Chips JU is secure, scalable, and accessible 24/7. The service shall include the provision of a user help desk

<sup>8</sup> Subject to a decision of the Governing Board of the Chips Joint Undertaking.

<sup>9</sup> See Chapter 4.

support, robust security measures, data backup and recovery, and regular maintenance and updates.

- The PCT shall continuously monitor the operation of the Design Platform and the quality of services provided to users. This includes incorporating user feedback loops and adopting corrective measures as necessary.

- The management and maintenance of a cloud-based repository for the European chip design community, populated with an extensive portfolio of open-source and proprietary 'design assets' to facilitate and enhance the design process for users, such as intellectual property (IP) blocks, design templates, fast adoption kits, process design kits (PDKs) from pilot lines and open foundries, open-source design tools, as well as reusable open-access design elements from previous EU-funded projects.

- A quicker and more efficient licensing process for commercial EDA tools and IP libraries, reducing burden and barriers for companies engaging in chip design, coupled with a startup support programme, that includes financing of licensing costs.<sup>10</sup>

- Integration in the Design Platform of the design support services provided by specialised design service providers, known as Design Enablement Teams, that will be designated following a subsequent linked call.<sup>11</sup>

- Advanced training and support services available to a wide range of users via the

Design Platform complementing the work of the network of Competence Centres

and/or potential future dedicated actions on design skills to support the development of

design skills across the Union.

The Design Platform is expected to support the design of a wide variety of technologies, specifically but not limited to digital circuits at multiple process nodes (up to leading edge nodes); analogue; mixed-signal; power; photonics and quantum. The Design Platform shall also support back-end of line (BEOL) design and manufacturing through advanced heterogeneous systems integration and advanced packaging techniques.

#### **2.4.3.** Scope

The purpose of this call is to select a consortium that will be responsible for implementing, hosting and running the Design Platform and coordinating its development, operation, and maintenance as well as related user support activities, in close collaboration with the Chips Joint Undertaking.

<sup>10</sup> The scope and budget for said start-up support programme is subject to an upcoming linked call, which is subject to a decision of the Governing Board of the Chips Joint Undertaking.

<sup>11</sup> Design Enablement Teams shall offer customised support to users throughout their entire chip development process. That will include running design tools and simulations on the cloud, design flow support and customisation, application engineering, access to Process Design Kits (PDKs) as well as prototyping and fabrication services from leading foundries and from the Chips for Europe Initiative pilot lines or other pilot lines.

To achieve those goals, proposals should address all of the following activities:

### 1. Comprehensive Planning and Development

- o Provide a comprehensive plan for the development and operation of the Design Platform, including clearly defined development and implementation targets, milestones, and key performance indicators (KPIs) for the platform's development and service delivery.

- The PCT shall seek to establish advisory groups comprising end-user companies, potential Design Enablement Teams, and other relevant stakeholders to provide critical insights and guidance throughout the development and operationalisation of the Design Platform. These advisory groups shall be particularly pertinent prior to the potential launch of future calls concerning Design Enablement Teams and eventually, user support.

## 2. Cloud service management